サイト内の現在位置を表示しています。

USB3.2 / 2.0デバイスIPコア

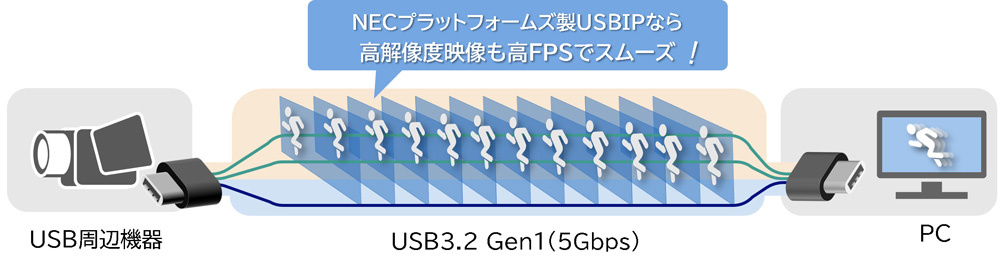

USBを使った映像伝送速度にお困りの方、USB3.2Gen2のケーブル長制限(1m以下)にお困りの方に、PCとの映像や大容量データの伝送向けに最適なFPGA用USB3.2 Gen1対応IPコアを提供します。AMD (Xilinx)・Altera®(Intel®)のFPGAに対応し、USB3.2 / USB2.0仕様に準拠したリンク層・プロトコル層を提供します。

特長

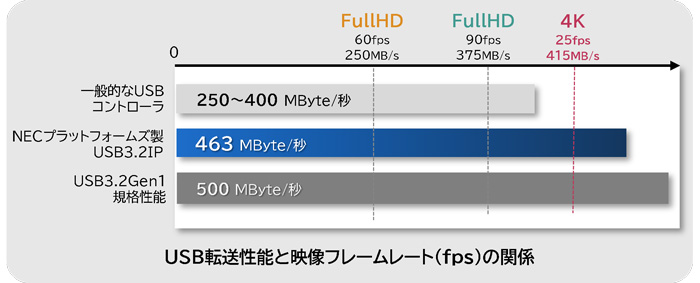

①転送性能460MByte/秒を実現

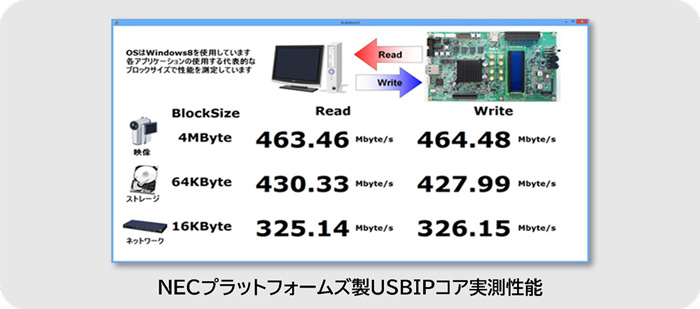

USB3.2Gen1(USB3.0)規格の上限500MByte/秒の92%に相当する463MByte/秒の転送性能を発揮します。USB3.0規格のメリットである2mケーブル長を維持しつつ、Full HD 解像度で100fps、4K解像度でも25fpsの映像伝送を実現可能です。

<計測条件>

【ホストPC】CPU : Intel® Core i7-3770/3.4GHz、Memory:8GB、OS :Windows®8 64Bit 版、xHCI ホスト:Intel® Q77 Express

【USB3.0デバイス】XC7Z045-1FFG900C(Zynq®-7045 AP SoC)、USB3.0 ベンダクラスファームウェア

②さまざまなUSB周辺機器

バルク・インタラプト・アイソクロナスの全てのUSB転送タイプに対応しているので、USBカメラ、USBストレージ、USBマイク・スピーカ、独自規格のUSB周辺機器開発に柔軟な対応が可能です。FPGAで主要周辺機器機能を実装している場合は、そのFPGAデバイスリソースを有効に活用し、省リソースで組込み可能です。

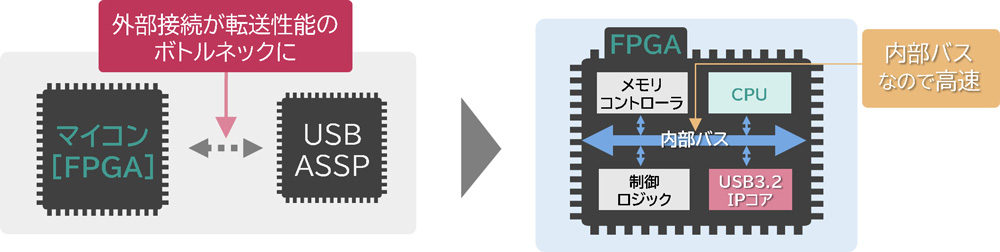

またFPGA内部バス(AXI/Avalon® Memory-Mapped Interfaces)で制御ロジックと接続でき、基板上/チップ間のバス幅/信号伝送速度の影響を受けないため、高速かつリアルタイム性を両立したUSB転送が可能となります。

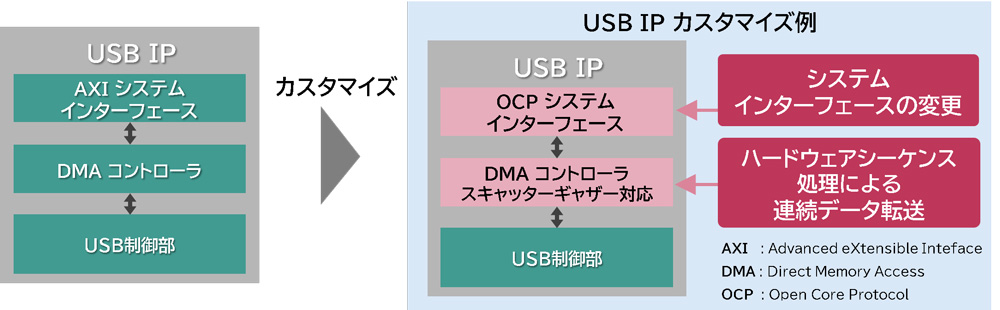

IPカスタム対応

- システムバスインターフェースを変更したい(カスタムインターフェース対応)

- さらに転送性能をチューニングしたい

- 専用装置向けに特殊プロトコルを追加したい

- さらに小さなゲート規模でFPGAに詰め込みたい

上記のような課題をお持ちの方、お気軽にNECプラットフォームズへご相談ください。

IPコア回路の全構成要素を、当社内のUSB開発経験豊富なエンジニアが開発しているため、さまざまなカスタム対応が可能です。お客様のご要望にあわせて、個別対応させていただきます。

国内技術者による開発サポート

お客様の開発にNetlist・ハードウェア・マニュアル・サンプルソフトウェアを提供することに加え、国内技術者がIP組込みに関する開発のサポートを行います。

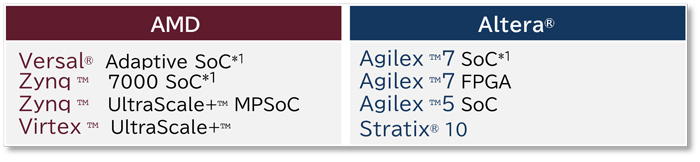

③AMD/Altera® FPGAデバイスに対応

AMD/Altera®からリリースされている、ARM®コア搭載最新FPGAにも対応しています。デバイス価格レンジも、ローエンドからハイエンドまでさまざまなデバイスに対応可能です。対応可能なデバイスの詳細はお問い合わせください。

搭載可能なFPGAのベースライン

ARM® コア搭載FPGAにIPコアを組込むことで、高速なUSB3.2デバイスを実現できます。

ARM® コア搭載FPGA・ハイエンドFPGA対応例

- *1USB2.0のみ内蔵のARM搭載FPGA

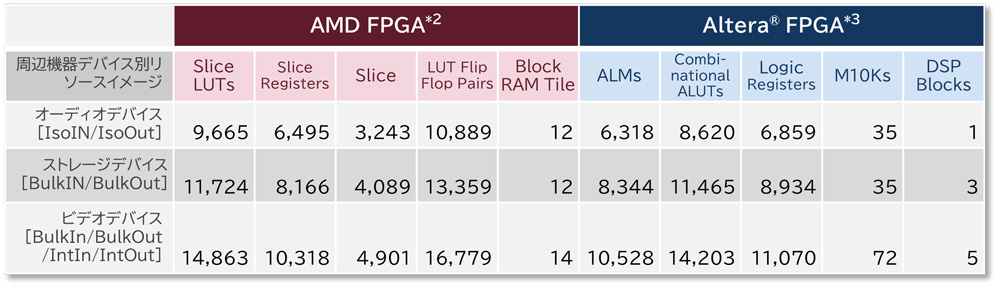

各種USB周辺機器に合わせて、エンドポイント構成を柔軟に変更可能です。FPGAリソースに合わせてバッファサイズなどのパラメータを変更し、お客様システムに組込むことが可能です。

周辺機器デバイス例とAMD/Altera®社FPGA必要リソース

- *2Artix™ 7 XC7A200TFBG676-1での合成結果

- *3Cyclone® V 5CGTFD7C5U19C7での合成結果

USB2.0デバイスIPのみのご提供も可能となりますので、さらに省リソースで低コストなFPGAに搭載することが可能です。

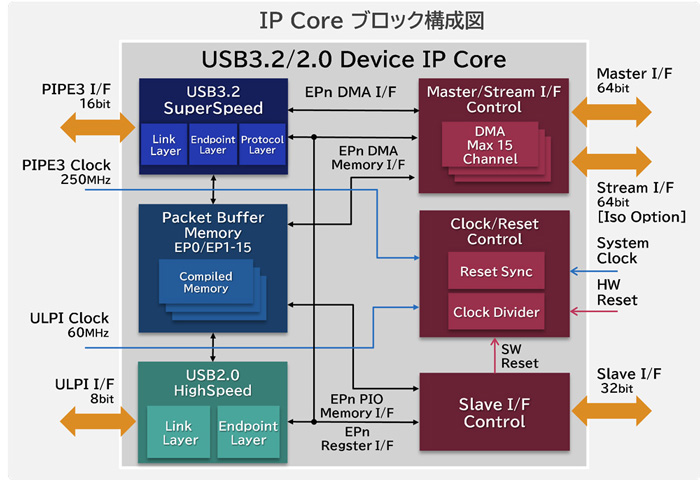

IPコア仕様(機能/API)・ブロック構成図

USB3.2/2.0デバイスIPコア仕様

- USB3.2 Gen1 [5Gbps対応] /USB2.0 [480Mbps対応] に準拠

- PHY Interface For the USB3.0 Architectures Version3.0 [PIPE 3.0] に準拠

パワーマネージメント

- Link Power Management U0~U3ステート

- U2 Inactivity Timeoutサポート

ループバックモード

- Link Training and Status State Machine

- Loopback Modeサポート

システムインタフェース仕様

- AXIデータバス幅64Bit [マスタ] /32Bit [スレーブ]

- ストリーム対応データバス幅64Bit

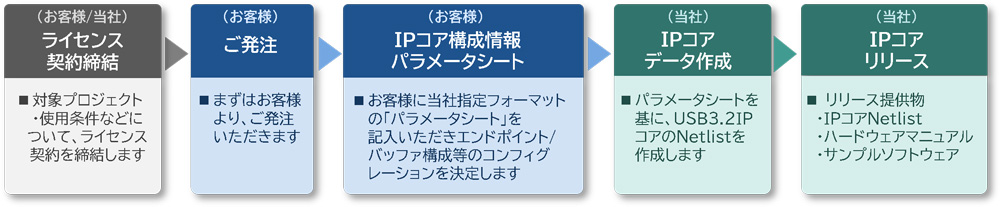

ご購入からリリースまでの流れ

エンドポイント/バッファなどご使用になられる構成を確認し、IPをコンフィグレーションしたうえでご提供いたします。

- ※AMD、Xilinx、Avalon®、Spartan™、Artix™、Versal®、Zynq™、Virtex™はAdvanced Micro Devices,Incの商標です。

- ※Intel®、Altera®、Avalon®、Cyclone®、Agilex™、Stratix®、MAX®は、アメリカ合衆国およびその他の国におけるインテルコーポレーションまたはその子会社の商標または登録商標です。

- ※ARM®はArm Limited(またはその子会社や関連会社)の登録商標です。

- ※その他掲載されている商標は、各社の商標または登録商標です。