サイト内の現在位置を表示しています。

FPGA設計

FPGA開発サービス産業機械・医療機器・モビリティ向けを中心に、エッジAI・高速インターフェース・画像処理をFPGAに最適化し、お客様の製品へ組込む開発サービスを提供します。

システム設計からFPGA設計、ボード設計、OSポーティング含めたソフトウェア開発、検証・評価、装置製造まで、ワンストップでお客様製品の開発をトータルにサポートします。

概要

FPGA回路設計

通信・画像・信号処理をはじめとする開発実績を基に、回路記述言語(RTL)による設計、高位合成ツールを使った設計など、お客様の製品に最適な設計手法で開発を行います。専門性の高い技術者による設計・検証で、高機能かつ高品質なFPGAシステムを構築します。

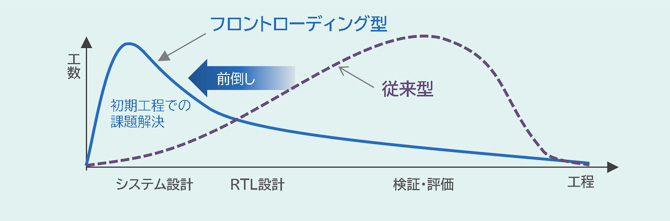

フロントローディング型のRTL設計

RTL設計では、前工程のシステム設計に負荷をかけDR(Design Review)を重視したフロントローディング型の開発を実施します。

高位合成による効率設計

| RTL設計 | 高位合成設計 | ||

| NEC CyberWorkBench | AMD Vitis HLS | ||

| 記述言語 | Verilog / SystemVerilog VHDL | C / SystemC | C |

|---|---|---|---|

| 特長 | タイミングやI/Fを完全に指定した回路設計 | デバイスを選ばずに合成。アルゴリズムだけでなく、制御回路も合成可能 | OpenCVなどをFPGAに合成できる関数群Vitis Libraryを利用可能 |

| 記述量 | 多い | 少ない | |

| 記述抽象度 | 低い FFは意図的に記述 |

高いが、高位合成を意識した記述も必要。 FFは制約により自動挿入。 | |

| シミュレーション | 遅い | アルゴリズムの検証はC言語で行うため非常に高速 | |

| 非同期回路 | コーディングルールに基づき非同期を設計。 静的検証の実施。 |

同期回路が前提 | |

FPGA設計

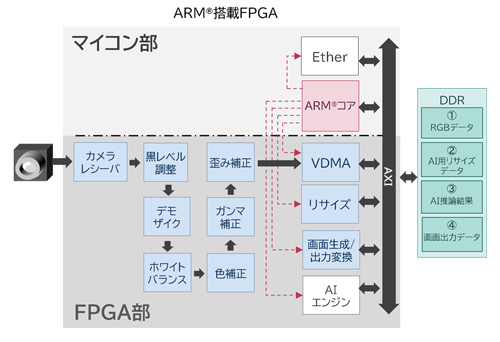

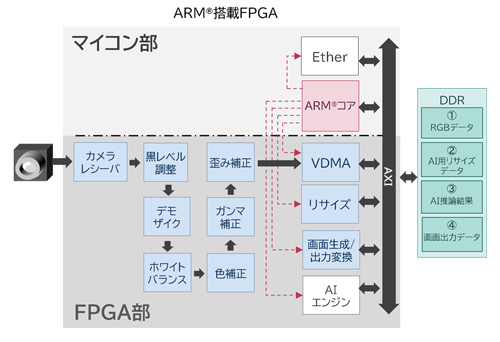

ARM®搭載FPGA開発技術

ARM®搭載FPGAにより、ワンチップで高速かつリアルタイム性の高いエッジシステムを実現します。標準搭載のUSBやEthernetに加え、カスタムインターフェースも対応可能です。

ARM®搭載FPGAを使うメリット

記述抽象度の高いC言語からRTLを自動生成する高位合成ツールを使い、効率的な設計を行います。

ARM®搭載FPGAを活かした高速・リアルタイム処理の実現

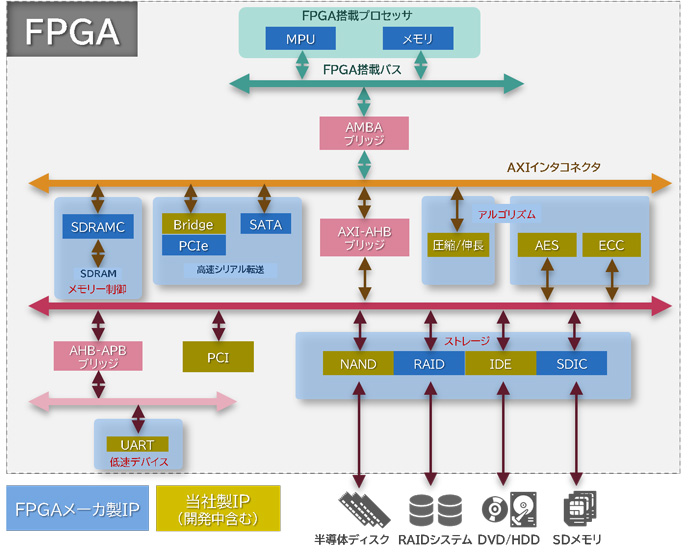

システムバス開発

豊富な開発実績をベースに、FPGAシステムに最適なバスシステムをご提供します。

AMBAバス開発

FPGAではデータの画像処理などの大量の繰り返し処理を、ARM®コアではシーケンス制御を主に担当させ、これらを協調動作させることで、ARM®搭載FPGAワンチップで低遅延と高い処理性能を実現します。

FPGA上にAMBAバスを構築し、お客様のARM®関連回路の資産を活用した開発をサポートします。

- お客様保有の設計資産や購入済みのIPコアに対応するAMBAバスを構成し、接続することが可能です。

- バス規格、および、お客様のLocal Bus仕様に基づいたインターコネクト回路やブリッジ回路を作成し、優先度による調停、排他制御等、お客様のご要望に柔軟に対応します。

- AMBA対応バス間のブリッジ回路の実装も可能です。また、ベンダ標準のブリッジ回路では性能が満たせないケースへ対応します。

Chip2Chipによる拡張接続

- ※AMDはAdvanced Micro Devices,Incの商標です。

- ※ARM®はArm Limited(またはその子会社や関連会社)の登録商標です。

- ※Avalon®は、アメリカ合衆国およびその他の国におけるインテルコーポレーションまたはその子会社の商標または登録商標です。

FPGAベンダー・IPベンダーのIPコア使用例

AIや画像処理など、さまざまな技術を持つIPベンダー様との協業を行っています。

最新技術を搭載したIPコアを使い、お客様の製品を開発します。

| Bus | 特徴 | データ幅 |

| Avalon | FPGA開発で広く使われる 互換性が限定 |

8-512bit、高帯域 |

| CHI (Coherent Hub Interface) | マルチコア及びアクセラレータ間のキャッシュコヒーレンシを提供 高度な設計・管理が必要 |

Max512bit、高帯域 |

|

ACE |

AXIプロトコルに追加されたキャッシュコヒーレンシを提供する拡張 |

32-1024bit、高帯域、高スループット |

|

AXI |

高性能 |

32-1024bit、高帯域、高スループット |

|

AHB |

中性能 |

32-128bit |

|

APB |

シンプルでペリフェラル用途 |

8-32bit、低帯域 |

|

OCP |

SoC設計向けのオープンプロトコル、汎用性と拡張性あり |

8-1024bit、低~高帯域 |

|

Aurora |

高速シリアル通信 |

Max 数100Gbps |

|

SPI |

シリアル通信 |

1bit、~数10Mbps |

|

I2C |

基盤上の短距離通信に最適 |

1bit、Max5Mbps |

|

CAN |

車載ネットワーク向け |

8byte、Max 1Mbps |

|

CAN-FD |

CANの拡張版 |

64bite、Max 8Mbps |

| 項目 | 対応内容 |

|

CPU |

ARMシリーズ |

|

リアルタイムOS |

NORTi |

|

Linux |

組込Linux(PetaLinux/Ubuntu他) |

|

開発ツール項目 |

対応内容 |

|

検証ツール |

Coverity(静的解析ツール) |

マイコン部 DSP ハードマクロ AIエンジン IPコアの仕様価格 入手性ライフサイクル 用途・環境パッケージサイズゲート数グレード SPAM Transceiver I/O など

- FPGA間を高速シリアルで接続することで、複数のFPGAを仮想的に一つのFPGAとして扱えます。

- 高性能なPCやGPUで行っていた高負荷処理を、エッジ端末に分散。低コストPCで制御可能なため、コストを抑えることが可能です。

- 光ファイバを使うことで長距離通信が可能。制御装置の設置可能な範囲が広がります。